11月30日消息,作为当下半导体晶圆代工领域的领军者,台积电的发展走向无疑备受瞩目。随着未来工艺节点逐步向1nm逼近,其是否还能持续推进技术迭代?让我们通过台积电最新公布的路线图一探究竟。

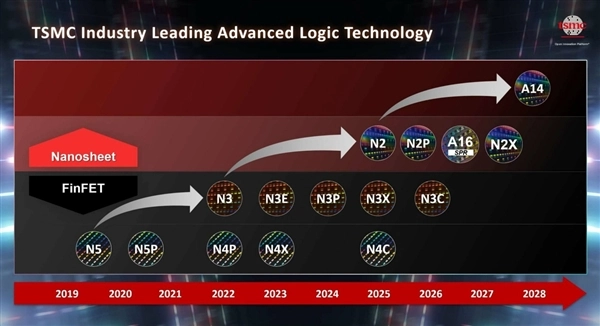

在开放创新平台生态系统论坛上,台积电发布了未来数年的逻辑工艺路线图,该路线图以2025年为核心节点。目前,其FinFET技术路线下正处于量产阶段的工艺为3纳米级别,具体涵盖N3、N3E、N3P、N3X以及N3C等版本。

2从2nm工艺节点起,芯片制造将采用Nanosheet晶体管——这正是GAA环绕栅极晶体管的实际应用形态。今年实现量产的是N2工艺,而率先确定采用该工艺的产品,出人意料地是AMD基于Zen6架构的EPYC处理器,不过这款处理器要到明年才会正式上市。

后续还会推出N2P和N2X工艺,不过在这两者之间会先有A16 SPR工艺。SPR是台积电的背面供电技术Super Power Rail的缩写,该技术与Intel的PowerVia据称存在较大差异,技术层面更为先进,但实际效果如何,还得等量产之后才能进行准确的对比。

A16 SPR原本对应的是最初规划的2nm工艺,不过在研发过程中经历了一些调整,台积电选择将GAA技术和背部供电技术分开进行量产,而非像三星、Intel那样在同一代工艺节点上同时实现这两项技术的量产。

再之后的A14节点会是一个重大更新,GAA与背部供电技术于一体,性能及能效更好看一些。

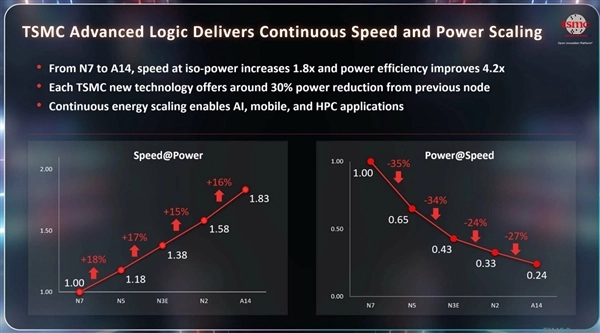

台积电发布这份技术路线图,意在向外界表明其具备在未来数年内实现工艺每年迭代的能力,并且每一代新工艺在性能与能效方面都能达成相近幅度的提升——此举核心是为了增强客户的信心。

以2018年推出的7纳米工艺节点N7作为参照标准来看,后续每一代芯片工艺在保持相同功耗水平的前提下,性能提升幅度基本处于15%至18%的区间范围内;与此同时,若维持性能不变,每一代工艺的功耗都能实现显著下降——从N7到N3的每一代,功耗降低幅度均超过三分之一,不过从N3到未来的A14工艺,每一代的功耗降低幅度则调整为四分之一左右。

对比N7,台积电提到A14工艺同功耗下提升83%的性能,能效则是3.2倍提升。

简单来说,在2018至2028这十年期间,芯片工艺的性能提升幅度大概在80%左右。若拿这个数据和摩尔定律作比较,结果无疑是令人沮丧的。但业内人士都明白,28纳米节点之后摩尔定律便慢慢失去了效力,所以能实现80%的性能提升其实已经相当难得。

2018年的N7工艺对应的处理器是苹果A12,其最高频率仅为2.5GHz,晶体管数量达69亿;而如今的A18 Pro处理器已实现4GHz的频率,晶体管数量更是达到200亿。按照目前的工艺迭代节奏,距离未来的A14节点还需经历两三代工艺的发展,届时实现5GHz频率、300亿晶体管规模的目标是值得期待的。